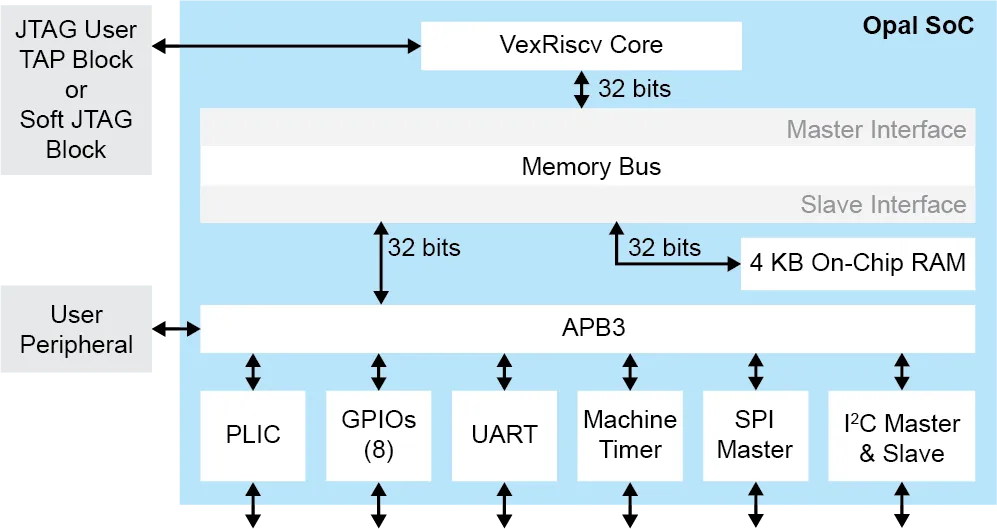

Efinix has announced three RISC-V Software-defined SoC's based on Charles Papon's VexRiscv core and optimized for the company's Trion T8 to T120 FPGA's.

VexRiscv is a 32-bit RISC-V CPU using RISCV32I ISA with M and C extensions, has five pipeline stages (fetch, decode, execute, memory, and writeback), and a configurable feature set. Each SoC includes a RISC-V core, memory, as well as various I/O and interfaces.

Opal SoC Block Diagram - Click to Enlarge

Key features for each of three RISC-V SoC's:

- Ruby SoC

- FPGA footprint - ~12K LEs/78 RAM blocks

- Performance - 50 MHz