Recently I was going through coverage topic where an expression like a+b was being covered. And earlier I had a doubt whether i can partially cover a variable. So went out to checkout all them doubs with a simple code.

module top;

logic clk=0;

logic a;

logic [1:0] b,c;

logic [7:0] d;

covergroup cg@(posedge clk);

option.auto_bin_max=32;

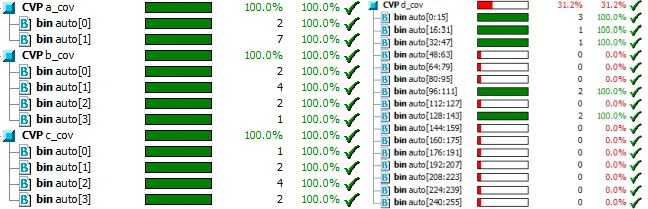

a_cov : coverpoint a;

b_cov : coverpoint b;

c_cov : coverpoint c;

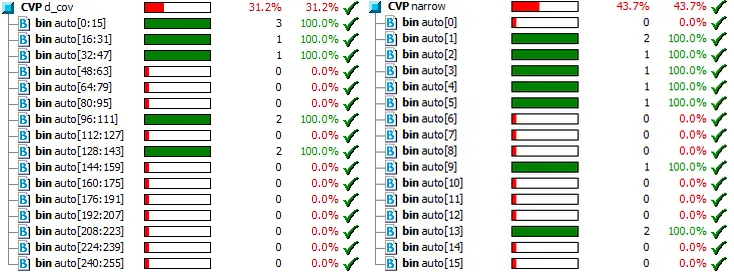

d_cov : coverpoint d;

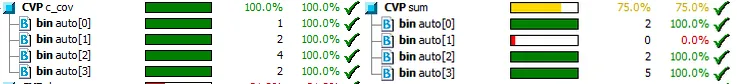

sum : coverpoint c+a;

expr : coverpoint (b&&c) + |d;

narrow: coverpoint d[3:0];

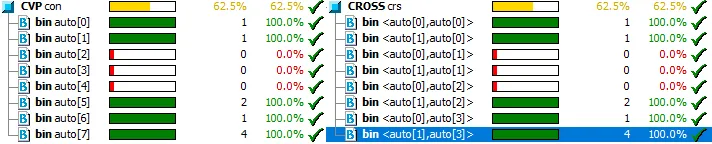

con : coverpoint {c+a,a};

crs : cross a_cov,sum;

endgroup

cg cg_h=new();

initial forever #5 clk=~clk;

always_ff @(posedge clk) {a,b,c,d} = $random();

initial #100 $finish;

endmodule

Note: option.auto_bin_max set to 32

sum coverpoint will have same bins as b_cov or c_cov, but will differ from c_cov because of the summation with a variable.

expr coverpoint will have same bins as sum because b&&c will result in a bit and |d into a bit and their sum as another bit. This way we can have any complex expression. This type of coverage is thus useful to check whether a case statement or loop and if blocks with complex expressions are being covered or not.

narrow coverpoint will only have 16 autobins unlike d_cov because it only covers d variable partially

Can we do cross coverage of two variable without using cross keyword?

Yes, ofcourse. But it will be cumbersome without cross coverage. We can just concatenate variables.